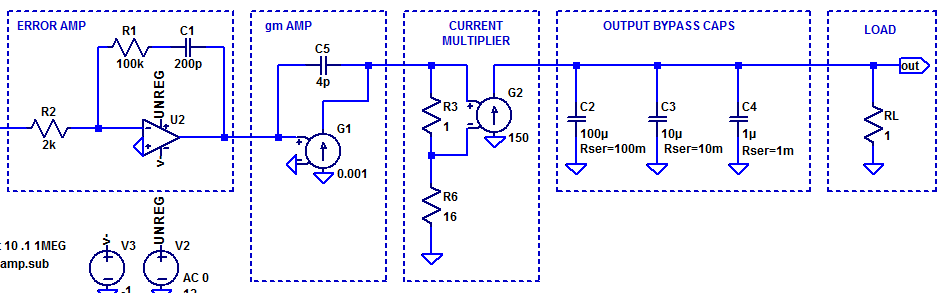

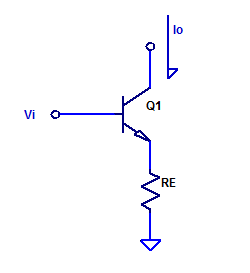

Continuing on from the analysis presented in low-noise-high-psrr-ldo-transconductance-gm-block, a simplistic trans-conductance amplifier can be constructed as shown in the figure below.

Forward trans-conductance from \( V_i \) to \( I_o \) was shown to be approximately,

$$ g_m = \dfrac{1}{R_E} \;\;\; \text{[A/V] } $$

For evaluation purposes, a \(g_m\) of 1 mA/V is chosen arbitrarily. The resistance of Re is then simply, Continue reading “Trans-conductance Amplifier Measurements”