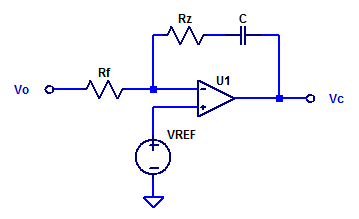

In this post we will develop and analyze a practical “type 2” error amplifier. The distinction of “type” 1, 2, or 3, is merely a description of how many poles are present in the compensator. All three types of error amplifiers will attempt to employ a pole at DC, i.e. operate as an integrator at low frequencies. Of course an error amplifier with an ideal integrator has a steady-state error of zero. However as is almost to all to common, digi-key does not stock any textbook class op-amps, with infinite differential gain and endless amounts of bandwidth.

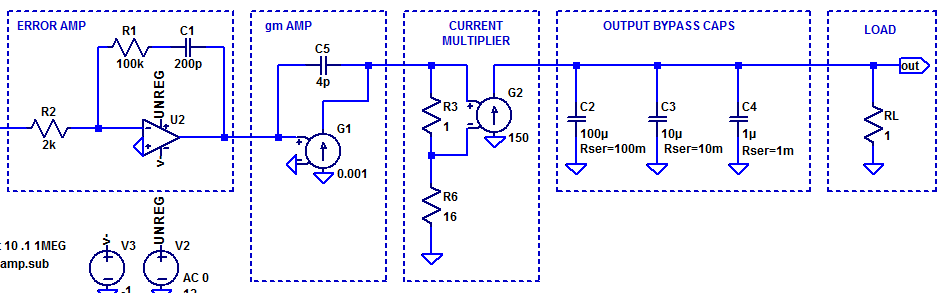

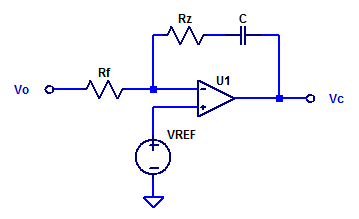

The figure below illustrates a practical type 2 error amplifier with voltage input and voltage output.

Continue reading “Low-Noise, High-PSRR LDO – Error Amplifier”